- 您现在的位置:买卖IC网 > Sheet目录3861 > PIC18F45K80-I/ML (Microchip Technology)MCU PIC 32KB FLASH 44QFN

2010-2012 Microchip Technology Inc.

DS39977F-page 115

PIC18F66K80 FAMILY

F9Fh

IPR1

PSPIP

ADIP

RC1IP

TX1IP

SSPIP

TMR1GIP

TMR2IP

TMR1IP

F9Eh

PIR1

PSPIF

ADIF

RC1IF

TX1IF

SSPIF

TMR1GIF

TMR2IF

TMR1IF

F9Dh

PIE1

PSPIE

ADIE

RC1IE

TX1IE

SSPIE

TMR1GIE

TMR2IE

TMR1IE

F9Ch

PSTR1CON

CMPL1

CMPL0

—

STRSYNC

STRD

STRC

STRB

STRA

F9Bh

OSCTUNE

INTSRC

PLLEN

TUN5

TUN4

TUN3

TUN2

TUN1

TUN0

F9Ah

REFOCON

ROON

—

ROSSLP

ROSEL

RODIV3

RODIV2

RODIV1

RODIV0

F99h

CCPTMRS

—

C5TSEL

C4TSEL

C3TSEL

C2TSEL

C1TSEL

F98h

TRISG

—

TRISG4

TRISG3

TRISG2

TRISG1

TRISG0

F97h

TRISF

TRISF7

TRISF6

TRISF5

TRISF4

TRISF3

TRISF2

TRISF1

TRISF0

F96h

TRISE

TRISE7

TRISE6

TRISE5

TRISE4

—

TRISE2

TRISE1

TRISE0

F95h

TRISD

TRISD7

TRISD6

TRISD5

TRISD4

TRISD3

TRISD2

TRISD1

TRISD0

F94h

TRISC

TRISC7

TRISC6

TRISC5

TRISC4

TRISC3

TRISC2

TRISC1

TRISC0

F93h

TRISB

TRISB7

TRISB6

TRISB5

TRISB4

TRISB3

TRISB2

TRISB1

TRISB0

F92h

TRISA

TRISA7

TRISA6

TRISA5

—

TRISA3

TRISA2

TRISA1

TRISA0

F91h

ODCON

SSPOD

CCP5OD

CCP4OD

CCP3OD

CCP2OD

CCP1OD

U2OD

U1OD

F90h

SLRCON

—

SLRG

SLRF

SLRE

SLRD

SLRC

SLRB

SLRA

F8Fh

LATG

—

LATG4

LATG3

LATG2

LATG1

LATG0

F8Eh

LATF

LATF7

LATF6

LATF5

LATF4

—

LATF2

LATF1

LATF0

F8Dh

LATE

LATE7

LATE6

LATE5

LATE4

—

LATE2

LATE1

LATE0

F8Ch

LATD

LATD7

LATD6

LATD5

LATD4

LATD3

LATD2

LATD1

LATD0

F8Bh

LATC

LATC7

LATC6

LATC5

LATC4

LATC3

LATC2

LATC1

LATC0

F8Ah

LATB

LATB7

LATB6

LATB5

LATB4

LATB3

LATB2

LATB1

LATB0

F89h

LATA

LATA7

LATA6

LATA5

—

LATA3

LATA2

LATA1

LATA0

F88h

T4CON

—

T4OUTPS3

T4OUTPS2

T4OUTPS1 T4OUTPS0

TMR4ON

T4CKPS1

T4CKPS0

F87h

TMR4

Timer4 Register

F86h

PORTG

—

RG4

RG3

RG2

RG1

RG0

F85h

PORTF

RF7

RF6

RF5

RF4

RF3

RF2

RF1

RF0

F84h

PORTE

RE7

RE6

RE5

RE4

RE3

RE2

RE1

RE0

F83h

PORTD

RD7

RD6

RD5

RD4

RD3

RD2

RD1

RD0

F82h

PORTC

RC7

RC6

RC5

RC4

RC3

RC2

RC1

RC0

F81h

PORTB

RB7

RB6

RB5

RB4

RB3

RB2

RB1

RB0

F80h

PORTA

RA7

RA6

RA5

—

RA3

RA2

RA1

RA0

F7Fh

EECON1

EEPGD

CFGS

—

FREE

WRERR

WREN

WR

RD

F7Eh

EECON2

Flash Self-Program Control Register (not a physical register)

F7Dh

SPBRGH1

EUSART1 Baud Rate Generator Register High Byte

F7Ch

SPBRGH2

EUSART2 Baud Rate Generator Register High Byte

F7Bh

SPBRG2

EUSART2 Baud Rate Generator Register Low Byte

F7Ah

RCREG2

EUSART2 Receive Register

F79h

TXREG2

EUSART2 Transmit Register

F78h

IPR5

IRXIP

WAKIP

ERRIP

TX2BIP

TXB1IP

TXB0IP

RXB1IP

RXB0IP

F77h

PIR5

IRXIF

WAKIF

ERRIF

TXB2IF

TXB1IF

TXB0IF

RXB1IF

RXB0IF

F76H

PIE5

IRXIE

WAKIE

ERRIE

TX2BIE

TXB1IE

TXB0IE

RXB1IE

RXB0IE

F75h

EEADRH

Data EE Address Register High Byte

F74h

EEADR

Data EE Address Register Low Byte

F73h

EEDATA

Data EE Data Register

F72h

ECANCON

MDSEL1

MDSEL0

FIFOWM

EWIN4

EWIN3

EWIN2

EWIN1

EWIN0

F71h

COMSTAT

RXB0OVFL RXB1OVFL

TXBO

TXBP

RXBP

TXWARN

RXWARN

EWARN

F70h

CIOCON

TX2SRC

TX2EN

ENDRHI

CANCAP

—

CLKSEL

F6Fh

CANCON

REQOP2

REQOP1

REQOP0

ABAT

WIN2/FP3

WIN1/FP2

WIN0/FP1

FP0

F6Eh

CANSTAT

OPMODE2

OPMODE1

OPMODE0

—/

EICOD4

ICODE2/

EICODE3

ICODE1/

EICODE2

ICODE0/

EICODE1

—/

EICODE0

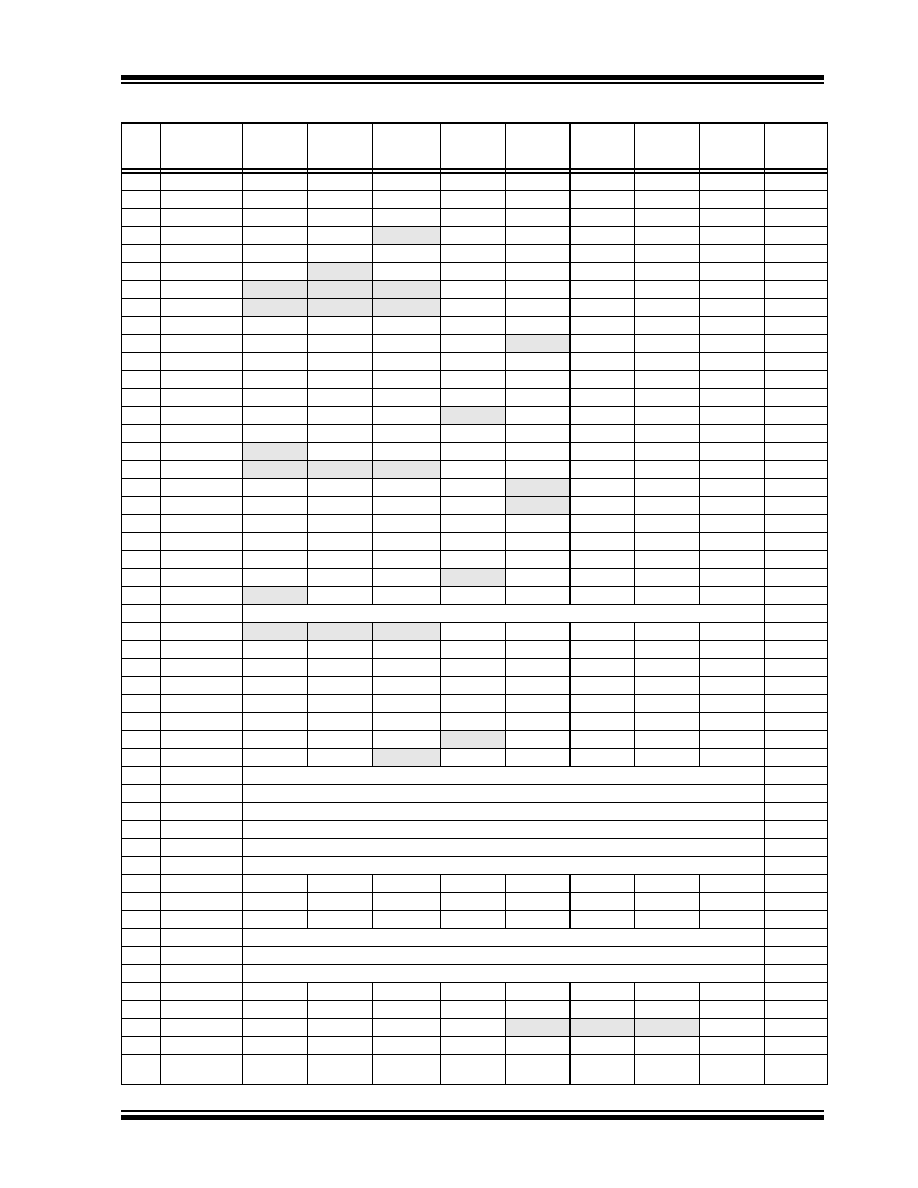

TABLE 6-2:

PIC18F66K80 FAMILY REGISTER FILE SUMMARY (CONTINUED)

Addr.

File Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on

POR, BOR

on page

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24F32KA302-I/ML

MCU 32KB FLASH 2KB RAM 28-QFN

PIC18LF45K80-I/ML

MCU PIC ECAN 32KBFLASH 44QFN

PIC18F4221-I/PT

IC PIC MCU FLASH 2KX16 44TQFP

PIC18F1320-I/SO

IC MCU FLASH 4KX16 A/D 18SOIC

PIC18LF2321-I/SS

IC PIC MCU FLASH 4KX16 28SSOP

PIC16F917-I/PT

IC PIC MCU FLASH 8KX14 44TQFP

PIC18F1320-I/SS

IC MCU FLASH 4KX16 A/D 20SSOP

PIC24FV32KA301-I/P

MCU 32KB FLASH 2KB RAM 20-PDIP

相关代理商/技术参数

PIC18F45K80-I/P

功能描述:8位微控制器 -MCU 32KB FL 4KBRM 16MIPS 12bit ADC CTMU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K80-I/PT

功能描述:8位微控制器 -MCU 32KB FL 4KBRM 16MIPS 12bit ADC CTMU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K80T-I/ML

功能描述:8位微控制器 -MCU 32KB FL 4KBRM 16MIPS 12bit ADC CTMU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F45K80T-I/PT

功能描述:8位微控制器 -MCU 32KB FL 4KBRM 16MIPS 12bit ADC CTMU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4610-E/ML

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4610-E/P

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4610-E/PT

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4610-I/ML

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT